PCB测试点设计与检测适配实操规范

PCB测试点(Test Point,TP)设计是 DFT(可测试性设计)体系中的关键环节,直接影响ICT针床测试覆盖率、飞针测试效率、FCT功能夹具设计、调试效率以及后期维修便利性。很多项目在样机阶段功能正常,但到了量产阶段才暴露出测试困难、治具成本高、误判率高的问题,根本原因往往就是测试点规划缺失。因此,测试点设计不能等PCB完成后再补,而应在原理图和Layout初期就同步纳入设计规范。

一、测试点设计的核心目标

测试点的首要任务是保证关键网络在生产、调试和售后阶段都能被快速接触和准确检测。建议优先覆盖以下几类网络。

1. 电源网络测试点

电源类网络必须优先预留测试点,包括输入电源VIN、12V、5V、3.3V、1.8V、参考电压VREF以及模拟/数字电源AVDD、DVDD。地线GND建议多点分布,便于不同区域测量。对于大电流电源路径,建议至少设置2~4个测试点,方便压降测试和回路分析。

2. 控制信号测试点

控制类信号主要用于调试和程序下载,包括MCU复位、BOOT启动、时钟、使能EN、中断线以及握手信号。这些点位在首板调试阶段价值极高,可以显著缩短软件联调和异常定位时间。

3. 通信接口测试点

UART、SPI、I2C、CAN、RS485、USB检测线等通信总线建议全部预留测试点。对于高速差分信号,如USB D+/D-、以太网差分对,不建议从主线额外拉长测试支线,避免阻抗失配和信号完整性下降。推荐在连接器附近或串联电阻位置做就近测试。

4. 模拟采样测试点

模拟部分测试点应重点放在ADC输入、运放输出、采样电阻两端、电流检测、温度采样节点等位置。这些点位直接关系到产品校准和失效分析效率。

二、测试点焊盘尺寸规范

测试点尺寸必须与检测方式匹配,否则会直接影响探针接触可靠性。

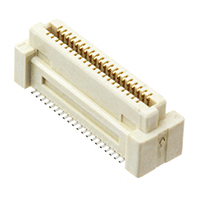

1. ICT针床测试

适用于中大批量生产,推荐焊盘直径控制在 0.8mm~1.0mm,最小不低于0.6mm。优先采用圆形裸铜焊盘,避免使用热焊盘连接方式,以减少探针接触电阻不稳定。

2. 飞针测试

适合样机和小批量,推荐尺寸为 0.5mm~0.8mm。高密度HDI板最小建议不低于0.4mm,否则飞针重复接触稳定性下降,容易造成开短路误判。

3. 人工调试测试

若测试点主要服务于示波器、万用表或逻辑分析仪,建议直径 1.0mm~1.5mm,必要时可采用环形孔测试点,便于探钩夹持。

三、测试点布局实操规范

测试点布局的好坏,决定治具能否顺利制作和量产效率。

1. 优先单面集中

量产板优先将测试点集中在PCB同一面,优先底面,便于ICT针床一次性覆盖。双面分布会显著增加夹具复杂度和成本。

2. 避开器件阴影区

测试点周围至少保持1.0mm以上净空,避免靠近高器件、散热片、电解电容、变压器、屏蔽罩等结构件,否则探针容易机械干涉。

3. 网格化排列

建议按2.54mm或1.27mm网格进行规则排布,方便针床治具统一布针,提高加工效率。

4. 边缘安全距离

测试点距离PCB边缘建议≥3mm,防止治具压板时受力不均导致边缘翘曲。

四、高速与敏感信号测试点设计要点

对于高速和敏感模拟信号,测试点不能简单理解为“拉一个焊盘”。

高速差分信号

USB、LVDS、以太网、PCIe等高速线禁止直接增加长Stub。建议采用以下方式:

串联电阻焊盘兼作测试点

连接器引脚附近测量

专用调试座

高频同轴座

模拟高阻节点

运放输入、基准源、高阻ADC输入等节点应避免大面积测试焊盘,否则会引入寄生电容和漏电误差。必要时通过0Ω电阻跳线转换为调试节点。

五、ICT / FCT / 飞针适配规范

不同测试方式,对测试点规划要求不同。

ICT适配

要求覆盖率优先达到 90%以上,尤其是:

所有IC电源脚

关键IO

上拉下拉网络

模拟采样链路

晶振回路辅助检测点

飞针适配

优先保证:

电源开短路检测

MCU烧录接口

通信接口

关键功能路径

FCT功能测试

建议增加夹具连接测试点,包括:

电源输入接口

按键模拟点

LED状态检测点

Relay反馈点

传感器输入点

六、常见设计失误与整改建议

实际项目中最常见的问题主要有以下几类。

1. 测试点过小

小于0.4mm时,飞针和ICT稳定性都会明显下降。

2. 分布过散

测试点遍布全板,导致针床面积增大,夹具成本翻倍。

3. 被器件遮挡

贴片器件底部、连接器内侧、散热器旁边的测试点基本不可用。

4. 高速信号乱加测试Stub

这是高速通信失效的高发原因之一。

5. 缺少GND参考点

没有足够地测试点,示波器测量容易引入误差和噪声。

售前客服

售前客服