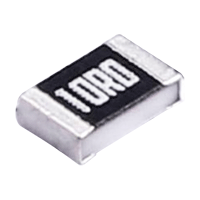

贴片电阻的信号完整性分析

在现代电子设计中,信号完整性(Signal Integrity, SI)是确保高性能电路稳定可靠运行的关键因素之一。信号完整性问题可能导致数据传输错误、信号失真和系统故障,尤其在高速数字电路、射频电路以及模拟信号处理系统中尤为重要。贴片电阻,作为一种常见的表面贴装元件,广泛应用于电流调节、分压、滤波和信号处理等领域。然而,在设计和应用中,贴片电阻的选择和布局对信号完整性有着显著影响。

本文将深入探讨贴片电阻对信号完整性的影响因素,包括寄生电容、寄生电感、阻抗匹配等,并提出优化设计和布局的建议,帮助工程师在电路设计中提高信号完整性。

一、贴片电阻的基本特性与信号完整性

1.1 贴片电阻的类型

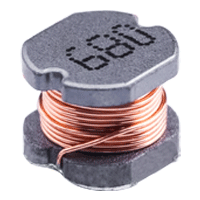

贴片电阻的种类繁多,主要包括以下几种:

薄膜电阻:采用薄膜工艺制造,具有较高的精度和稳定性,适用于高频和高精度应用。

厚膜电阻:通过印刷技术制造,成本较低,适合一般应用。

金属膜电阻:采用金属膜技术,具有良好的温度系数和频率特性,常用于高频电路。

1.2 信号完整性的概念

信号完整性是指在信号传输过程中,信号波形保持其形状、幅度和时间关系的能力。信号完整性问题通常表现在以下几个方面:

信号失真:由于元件的寄生参数导致信号波形发生变化。

反射:不匹配的阻抗导致信号反射,影响信号传输。

串扰:相邻信号线之间的耦合效应,导致信号干扰。

地回路问题:地电位差引起的信号波形变化。

在贴片电阻的设计中,这些因素会对信号完整性产生重要影响。

二、贴片电阻对信号完整性的影响

2.1 寄生电容的影响

寄生电容是贴片电阻在电路中不可避免的一个特性。每个电阻器都有其自身的寄生电容,通常在几皮法(pF)范围内。在高速信号传输中,这种寄生电容会对信号波形产生影响,导致以下问题:

信号延迟:寄生电容会造成信号上升和下降时间的延迟,影响信号传输的时序。

波形失真:在高频信号下,寄生电容会与电阻形成RC低通滤波器,削弱高频成分,导致信号失真。

2.2 寄生电感的影响

与寄生电容相对应,贴片电阻同样存在寄生电感。寄生电感在电流变化时会产生感应电压,影响信号传输。其主要影响包括:

高频响应降低:寄生电感会对高频信号的传输造成衰减,导致信号幅度降低。

阻抗变化:在高频下,贴片电阻的等效阻抗会受到寄生电感的影响,造成信号反射和失真。

2.3 阻抗匹配

在信号传输过程中,阻抗匹配是确保信号完整性的重要因素。若贴片电阻的阻抗与信号线路的特性阻抗不匹配,会导致信号反射和串扰。具体来说:

反射系数:反射系数是量度信号反射强度的参数,其计算公式为:

R=ZL+Z0ZL−Z0

其中,ZL为负载阻抗,Z0为传输线的特性阻抗。信号反射将导致波形失真。

阻抗匹配技巧:为提高信号完整性,设计中可通过调整电阻值、选择适当的阻抗匹配网络来实现信号的阻抗匹配,减少反射。

2.4 串扰现象

串扰是指一个信号线上的信号通过电容或电感耦合到相邻信号线上,造成信号干扰。在贴片电阻布局中,若相邻信号线距离过近,可能会导致串扰效应增强,影响信号的可靠性。

减小串扰的措施:可以通过增加信号线间距、使用屏蔽层或选择适当的电阻布局设计来减小串扰。

三、提高贴片电阻信号完整性的设计策略

为了提高贴片电阻的信号完整性,设计过程中需考虑以下策略:

3.1 优化布局设计

贴片电阻的布局对信号完整性影响显著。优化布局可以减少寄生参数的影响,具体措施包括:

缩短信号路径:尽量将贴片电阻放置在离信号源和负载较近的位置,减少信号传输距离。

避免交叉布线:信号线之间应保持一定距离,避免交叉,以减小串扰。

3.2 选择合适的贴片电阻

在选择贴片电阻时,需考虑以下因素:

高频性能:选择高频特性优良的贴片电阻,如薄膜电阻,以减小寄生电感和电容。

功率额定值:确保选择的电阻功率额定值适应电路要求,避免过热。

3.3 使用适当的阻抗匹配网络

在高频信号传输中,设计适当的阻抗匹配网络可有效降低反射损失。常见的阻抗匹配方法包括:

使用匹配电阻:在信号源和负载之间加入额外的匹配电阻,以实现阻抗匹配。

LC匹配网络:通过设计LC网络进行阻抗转换,优化信号传输。

3.4 进行仿真分析

在电路设计过程中,使用电磁仿真软件进行信号完整性分析可以帮助识别潜在问题。常见的软件包括:

HFSS(高频结构仿真)

ADS(先进设计系统)

SPICE(模拟电路仿真)

通过仿真分析,工程师能够在设计阶段发现并解决信号完整性问题,减少后期调试的工作量。

四、实例分析:贴片电阻在数字电路中的应用

4.1 应用背景

在数字电路中,贴片电阻的信号完整性直接影响数据传输的可靠性。以一个高速数字信号传输系统为例,探讨贴片电阻的应用及其信号完整性分析。

4.2 电路设计

假设某高速数字电路工作频率为1GHz,信号路径设计中使用了多种贴片电阻。设计过程中需要确保信号传输的完整性,避免由于寄生效应造成的信号失真。

4.3 信号完整性分析

在设计阶段,使用仿真工具进行信号完整性分析,发现以下问题:

信号上升时间过长:由于寄生电容的影响,信号的上升时间达到10ns,影响了数据传输的速率。

反射损失明显:在阻抗不匹配的情况下,信号反射导致幅度降低20%,影响了接收端的信号强度。

4.4 优化方案

为了解决上述问题,采取了以下优化措施:

更换高频贴片电阻:选择更低寄生电容的薄膜电阻,优化信号的上升和下降时间。

调整电路布局:缩短信号路径,将贴片电阻放置在信号源和负载之间,减小信号传输延迟。

加入匹配电阻:在信号线末端加入匹配电阻,以实现更好的阻抗匹配,减少信号反射。

4.5 优化效果评估

通过再次仿真分析,优化后信号的上升时间缩短至5ns,反射损失降低至5%。信号的完整性得到了显著提升,满足了高速数据传输的要求。

五、结论

贴片电阻在电路设计中扮演着至关重要的角色,尤其在高速数字电路中,其对信号完整性的影响不容忽视。通过分析贴片电阻的寄生电容、寄生电感、阻抗匹配和串扰等因素,工程师可以更好地理解其对信号完整性的影响,并采取有效的优化措施。

在未来的电子设计中,随着信号频率的不断提升和系统集成度的增加,对贴片电阻信号完整性的研究将更加深入。合理的设计和布局策略将有助于确保高性能电路的稳定性和可靠性,为电子技术的进步提供坚实的基础。

售前客服

售前客服